Đăng nhập

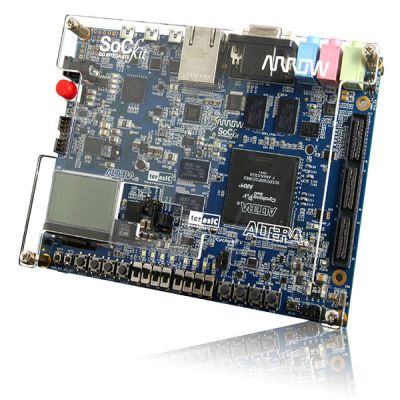

DE0-Nano-SoC Kit/Atlas-SoC Kit

2.500.000đ

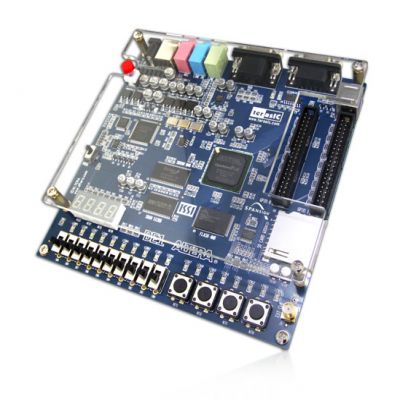

DE10-Nano Kit

3.299.000đ

DE1-SoC Board

5.975.000đ

DE10-Standard

8.499.000đ

Altera DE1 Board

3.599.000đ

DE0-Nano Development and Education Board

2.000.000đ

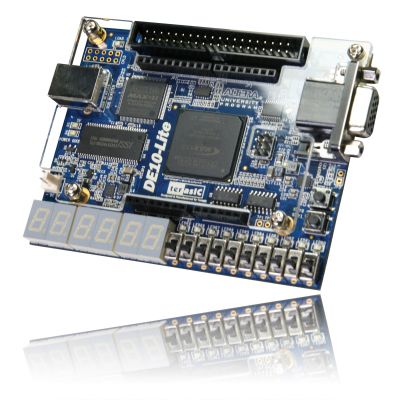

DE10-Lite Board

2.039.000đ

The model HSRFS_500-Digital_XCZU28DR is based on Zynq UltraScale+ RFSoC. The ZCU111 Evaluation Solution provides a rapid, comprehensive RF Analog-to-Digital signal chain prototyping platform.

The Zynq® UltraScale+™ RFSoC ZCU111 Evaluation Kit enables designers to jumpstart RF-Class analog designs for wireless, cable access, early-warning (EW) radar and other high-performance RF applications. This kit features a Zynq UltraScale+ RFSoC supporting 8x 4GSPS 12-bit ADCs, 8x 6.5GSPS 14-bit DAC, and 8 soft-decision forward error correction (SD-FECs). Complete with ARM Cortex A53 and ARM Cortex-R5 subsystems, UltraScale+ programmable logic, and the highest signal processing bandwidth in a Zynq UltraScale+ device, this kit provides a rapid, comprehensive RF Analog-to-Digital signal chain prototyping platform.

This will be used in Digital control in HSRFS system

Application Processing Unit (APU)

· 64-bit quad-core Arm Cortex-A53 MPCores. Features

associated with each core include:

o Arm v8-A Architecture

o Operating target frequency: up to 1.3GHz

o Single and double precision floating point:4 SP / 2 DP FLOPs

o NEON advanced SIMD support with single and double precision floating point instructions

o A64 instruction set in 64-bit operating mode, A32/T32 instruction set in 32-bit operating mode

o Level 1 cache (separate instruction and data, 32KB each for each Cortex-A53 CPU)

– 2-way set-associative Instruction Cache with parity support

– 4-way set-associative Data Cache with ECC support

o Integrated memory management unit (MMU) per processor core

o TrustZone for secure mode operation

o Virtualization support

· Ability to operate in single processor, symmetric quad processor, and asymmetric quad-processor modes

· Integrated 16-way set-associative 1MB Unified Level 2 cache with ECC support

· Interrupts and Timers

o Generic interrupt controller (GIC-400)

o Arm generic timers (4 timers per CPU)

o One watchdog timer (WDT)

o One global timer

o Two triple timers/counters (TTC)

RF-ADC Features· Tile oriented

o Four RF-ADCs and one PLL per tile

o 12-bit or 14-bit resolution

· Decimation filters

o Full bandwidth data-rate support

o 80% pass band, 89dB stop-band attenuation

· Mixer

o Full complex mixers

o 48-bit NCO per RF-ADC

o Fixed Fs/4, Fs/2 low-power mode

· Single/multiband flexibility

o 2x bands per 2.058GSPS, 2.220GSPS, or 2.5GSPS RF-ADC pair

o Can be configured for real or imaginary (I/Q) inputs

· Signal amplitude threshold

o Two programmable flags per RF-ADC

· Quadrature modulator correction

o Gain/phase/offset correction per RF-ADC pair

· Multi-chip synchronization

· Flexible interconnect logic interface

o N words x frequency selection

o On-chip clock forwarding (Gen 3 devices)

RF-DAC Features

· Tile oriented

o Four RF-DACs and one PLL per tile

o 14-bit resolution

o 4GHz full power output bandwidth

o Up to 5GHz RF output

· Interpolation

o Full bandwidth data rate support

o 80% pass band, 89dB stop band attenuation

· Mixing

o Full complex mixers

o 48-bit NCO per RF-DAC

o Fixed Fs/4, Fs/2 low-power mode

o 1st/2nd Nyquist zone RF-DAC operation support

· Single/multiband flexibility

o 2x bands per RF-DAC pair

o Can be configured for real or imaginary (I/Q) outputs

· Quadrature modulator correction

o Gain/phase/offset correction per RF-DAC pair

· Sinx/x correction

· Sample delay correction

· Multi-chip synchronization

· Flexible interconnect logic interface

· N words x frequency selection

· On-chip clock forwarding (Gen 3 devices

ENVIRONMENTAL CHARACTERISTICS (Design to Meet)| Parameter | Minimum | Typical | Maximum | Units | Notes |

| Operating Temperature | -40 | 50 | °C | ||

| Non-operating Temperature | -45 | 65 | °C | Storage | |

| Relative Humidity (non-condensing) | 5 | 95 | % |

Absolute Maximum Rating

| Input RF drive level without damage | +5dBm@6GHz, +10dBm@18GHz | Maximum |

| Load VSWR @ POUT =30W | 5:1 @ all load phase & amplitude continuous More than 6:1 may cause PA damage |

Storage |

| Over Temperature | 80°C @ heatsink | Storage |

Sản phẩm liên quan

1.1. Center Digital Signal Processing System

THÔNG TIN KHÁCH HÀNG

ĐỊA CHỈ GIAO HÀNG

HÌNH THỨC THANH TOÁN

Ngân hàng TMCP quân đội- CN Hoàn Kiếm

Chi nhánh:Ngân hàng TMCP quân đội- CN Hoàn Kiếm

Tên chủ tài khoản: cty cổ phần tích hợp và giải pháp doanh nghiệp Việt nam

Số tài khoản: 0571103179006

1.1. Center Digital Signal Processing System

THÔNG TIN KHÁCH HÀNG

- Họ và tên:

- Điện thoại:

- Email:

ĐỊA CHỈ GIAO HÀNG

- Địa chỉ:

- Quận / huyện:

- Tỉnh / thành phố:

- Phí vận chuyển:

- Ghi chú:

HÌNH THỨC THANH TOÁN